Implementation of logic gates pdf

Implementation of logic gates pdf

logic gates using Taffoli gates. The architecture of binary multiplier is specially designed to make them suitable The architecture of binary multiplier is specially designed to make them suitable for reversible logic implementation.

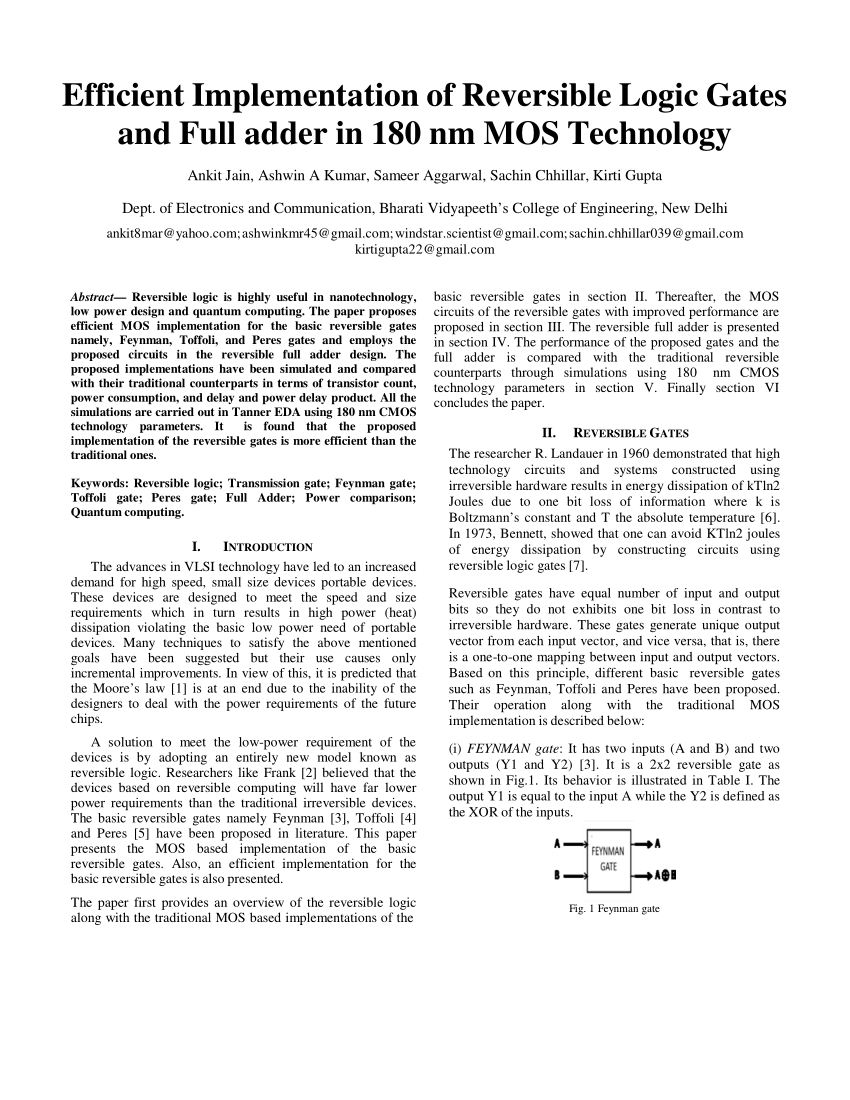

There are many types of reversible logic gates currently being used .eg fennyman gate, toffoli gate, peres gate etc. For our implementation we have used Peres reversible logic gate.

that when the data select input, A is LOW at logic 0, input I1 passes its data through the NAND gate multiplexer circuit to the output, while input I0 is

present the simulation of NAND and NOR logic gate by CMOS and PFAL logic moreover with the help of simulated result by OrCAD PSPICE tool, it can be shown that the NAND & NOR used with adiabatic logic can reduce the power dissipation effectively than conventional CMOS circuit. Key Words: Low Power, Adiabatic Circuits, Logic Gates. 1. INTRODUCTION With the cultivation of VLSI technology …

The action of the c-NOT logic gate is to swap two of the spin populations. Logic gates such as these, which can be expressed as a truth table and which are unitary, are necessarily permu-

A NOR gate is a logic gate which gives a positive output only when both inputs are negative. Like NAND gates, NOR gates are so-called “universal gates” that can be combined to form any other kind of logic gate.

The implementation of all optical NAND logic gate is one of the most important aspects. The universal logic gate is one of the most essential logic gates. Hence, it is interesting to implement the NAND logic functionality in the optical domain using the micro-ring resonator structure. However, the symbol and truth table of NAND logic gate can be represented by the Fig.

Steps to be followed in the process of implementation of Logic Gates: Step 1: For NAND implementation, add Bubbles at the outputs of AND gates and at the inputs of OR gates.

A.Veera Lakshmi et al Low Power Implementation of Sequential Circuits using Reversible Logic Gates

3 Electronic Science Digital Electronics 5. Logic gates • ON or OFF describes the switch position. The common use of logic gate is to act as switches (although they have no moving parts).

designed the various Domino logic gates such as AND, OR, NAND, NOR and here we have analyzed the performance of these gates in the terms of number of transistors, area, and Power.

377 Figure 1. Structured diagram of the logic gate minimisation package Figure 2. Minimised output expression and logic gate diagram

Chapter 6 Implementation of Logic Circuits with Standard Logic Chips Once logic circuits have been designed with generic logic devices, the next step is to implement the design in physical hardware. The first approach we will study is to use standard logic chips, integrated circuits that contain a small number of logic devices. The second approach, using programmable logic hardware, will be

QCA cell-based structures can implement the logic gates, wires, memory units, combinational and sequential logic circuits. Digital logic design employing QCA cell is the main focus of this paper. In this paper, structure for Exclusive OR operation is proposed with primary goal of application in adder circuit to reduce the area. QCA designer is the EDA tool used for implementation and

CMOS VLSI is thedigital implementation technology of choice for the foreseeable future (next 10-20 years) For other gates, Logical Effort is ratio of logic gate’s input 2 2 2 – –) – – – – – – –

4 × 4 bit Vedic multipliers using reversible logic gate. Design and implementation of 2 × 2 and 4 × 4 bit vedic multiplier using irreversible logic gates Vedic multiplier technique is used to perform multiplication operation in a faster way as compared to usual multiplication approach. In this paper we tried to implement the same not using irreversible gates but with reversible gates [5-7

The reversible logic gates will be having n-input and n-output i.e. equal number of input and equal number of output, and also with one-to-one mapping i.e. inputs can …

Implementation of threshold logic gates using RTDs

Vol. 5 Issue 5 May 2016 Design and Implementation of CLA

Boolean logic in the form of simple gates is very straightforward. From simple gates you can create more complicated functions, like addition. Physically implementing the gates is possible and easy. From those three facts you have the heart of the digital revolution, and you understand, at the core, how computers work.

The XOR and XNOR logic gates implementation consists of two MZI structures as shown in Fig. 3. The continuous optical signal of wavelength λ is applied at the input port of MZI 1. Here, no signal is provided at the second input terminal of MZI 1.

International Journal of Advanced Technology in Engineering and Science www.ijates.com Volume No 03, Special Issue No. 01, March 2015 ISSN (online): 2348 – 7550

In this paper, Threshold logic gates (TLG) are implemented using Resonant Tunneling Diodes (RTD). TLG is conceptually similar to the early McCulloch-Pitts model of the neuron and is normally used

Experiment 2 Basic Logic Gates Implementation Using Breadboards and Discrete Gates Introduction:Introduction: Logic functions can be implemented in several ways.

2/01/2017 · IMPLEMENTATION OF BOOLEAN EXPRESSION USING UNIVERSAL GATES(NAND/NOR) GATE BUS ADDA. Loading… Unsubscribe from GATE BUS ADDA? Cancel Unsubscribe. Working… Subscribe Subscribed Unsubscribe 8.7K

A reversible gate has the equal number of inputs and outputs and one-to-one mappings between input vectors and output vector, thus the vector of input states can be always reconstructed from the vector of output states. A gate with k inputs and k outputs is called a k*k gate. Reversible logic Gate has one of the most important approaches for the power factor with its application in low power

7/03/2014 · IMPLEMENTATION OF BOOLEAN FUNCTIONS IN SUM OF PRODUCT FORM BY NAND GATES.

Digital Logic Design: Previous: AND OR NAND XOR XNOR Gate Implementation and Applications: Next >>> CS302 – Digital Logic & Design. Lesson No. 06. LOGIC GATES & OPERATIONAL CHARACTERISTICS. NOR Gate as a Universal Gate. The NOR gate is also used as a Universal Gate as the NOR Gate can be used in a. combination to perform the function of a AND, OR and NOT gates. 4. NOT Gate Implementation…

Page 191 Design and Implementation of Sequential Counters Using Reversible Logic Gates with Mach-Zehnder Interferometer A.Rudramadevi M.Tech(ES & VLSI Design),

Realization of Logic Gates Using Mcculloch-Pitts Neuron Model J.S.Srinivas Raju1, Satish Kumar2, logic gate performances by using MCP model easily process of making and braking connections in Network solutions and solution of Hebb nets for REFERENCES [1] Neural Networks, Fuzzy Logic, and Genetic Algorithms by S.Rajasekharan and G.A Vijayalakshmi Pai. [2] OR GATE, Hyperphysics.phy …

CSEIT172551 Received : 10 Sep 2017 Accepted : 17 Sep 2017 September-October-2017 [(2)4: 243-247] International Journal of Scientific Research in Computer Science, …

International Journal of Advanced Technology & Engineering Research (IJATER) ISSN NO: 2250-3536 VOLUME 2, ISSUE 3, MAY 2012 158

implementation of logic gates using mux Q- Using 2 to 1 MUX implement the following 2-input gates: (a) OR (b) AND (c) NOR (d) NAND (e) XOR (f) XNOR (g) NOT. Ans: To implement the above for every gate, either we can derive the different gates using the logic (the truth table) or the procedure to implement any function with MUX (discussed earlier)

But with the applications of Boolean gates like Adders, Subtractors, Counters and so on it is possible to create almost any logic. With this post, we are going to help you and thus understand better, the logic behind using gates. The steps are simple and creative. But for the implementation requires a relay and a 6 volt battery. The very first implementation of Boolean gates also included

Diode logic gates use diodes to perform OR and AND logic functions as shown in the circuit diagram. Connection of the LED at the output is optional which simply displays

Journal of Network Communications and Emerging Technologies (JNCET) www.jncet.org Volume 6, Issue 12, December (2016) ISSN: 2395-5317 ©EverScience Publications 20

2b. The implementation of a NAND gate is shown in Fig 2c. An OR gate is realized by connecting two new reversible gates as shown in the Fig 2d shown in the Fig 2d.

Implementation of threshold logic gates using RTDs Journal of Electronic and Electrical Engineering, ISSN: 0976–8106 & E-ISSN: 0976–8114, Vol. 1, Issue 2, 2010

Creation of entanglement and implementation of quantum logic gate operations using a three-dimensional photonic crystal single-mode cavity Durdu Ö.

Reversible implementation is done using a BVPPG gate, three Peres gates and a Feynman gate as shown in fig 5. BVPPG gate generates two partial products among which, one is Q0. Q1 is obtained from one of the Peres gates and Q2, Q3 are the outputs from Feynman gate. This design needs five reversible logic gates, five constant inputs and generates five garbage outputs. Quantum cost and …

Combinational Logic Implementation z Two-level logic y Implementations of two-level logic y NAND/NOR z Multi-level logic y Factored forms y And-or-invert gates z Time behavior y Gate delays y Hazards z Regular logic y Multiplexers y Decoders y PAL/PLAs y ROMs CS 150 – Sringp 0012 – Combinational Implementionta – 2 Implementations of Two-level Logic z Sum-of-products y AND gates …

Implementation of Advanced encryption Standard using Reversible Logic Gate D Srinivas1, Boda Aruna2, Ravi Boda3 1 Department of ECE, VJIT, Hyderabad, India 2 Department of ECE, MIETW, Hyderabad, India 2Department ECE, University College of Engineering, Osmania University, India Abstract: The Rijndael cryptosystem is a new Advanced Encryption Standard (AES) till now many …

Design and Implementation of Adiabatic based Low Power

CprE 210 Lec 15 1 • Multiplexers are circuits which select one of many inputs • In here, we assume that we have one-bit inputs (in general, each input may have more than one bit)

Memristor-CMOS (MeMOS) logic based adder circuit that can be used in based logic computational architectures. I I have also analyzed the transient response of logic gates designed using MeMOS logic …

III.1A Digital logic gates Combinational Digital gates are circuits that pass or block signals moving through a logic circuit. NOT gate Fig. 9 XOR design with NAND and NOR gates 1 Hence the following implementation constitutes a half adder circuit. A 1 B 1 A 1 B 1 A B 1 A 1 +B 1 A B 1 1 C1 S1 Fig. 10 Half adder circuit. FULL ADDER Task: Build the circuit below and verify that it works as a

The basic logic gates can be combined to form more complex digital circuits of all types. In fact, the NOT and AND gates alone are sufficient, but that does not really concern us… Computer Science Dept Va Tech October 2003 ©2003 McQuain WD & Keller BJ Logic Gates 3 OO Software Design and Construction Modeling a Logic Gate Consider the fundamental characteristics of the logic gates …

– practicing the implementation of multiple input AND and OR functions using degenerate two-level logic circuit forms, – gaining a close insight into the functioning and properties of decoder circuits,

Implementation of Ternary Logic Gates using CNTFET Rahul A. Kashyap1 1 fundamental gates in a ternary logic system are the inverter, NOR and NAND gates respectively. The ternary logic levels and values are shown in Table I. Voltage Level Logic Value 0 0 1/2V dd 1 V dd 2 Table. 1 : Logic Values A. Ternary Inverter A Ternary Inverter is a fundamental gate in ternary logic system. A general

Ternary logic gates are the basic building blocks in realizing combinational and sequential logic functions. The implementation is based around (bipolar transistors, MOSFETs etc.) a basic switching elements, which is referred to as T-Gates . The Ternary gate called T-gate qualifies as a universal element in several different senses. Firstly, it should be logically complete with simple

NOR logic Wikipedia

Construction and Implementation of NMR Quantum Logic Gates

/International Journal Of Computational Engineering

Implementing Gates Boolean Logic Implementation

Implement Logic Gates Electronic Circuits and Diagrams

Implementation of all-optical NAND logic gate and half

VHDL Implementation of Reversible Logic Gates

Design and Implementation of Ternary Logic Gates over a

IMPLEMENTATION OF VEDIC ULTIPLIER USING REVERSIBLE GATES

explorerootsimplementation of logic gates using MUX

Design and Implementation of Logic Gates using Artificial

Implementation of threshold logic gates using RTDs

explorerootsimplementation of logic gates using MUX

The basic logic gates can be combined to form more complex digital circuits of all types. In fact, the NOT and AND gates alone are sufficient, but that does not really concern us… Computer Science Dept Va Tech October 2003 ©2003 McQuain WD & Keller BJ Logic Gates 3 OO Software Design and Construction Modeling a Logic Gate Consider the fundamental characteristics of the logic gates …

Page 191 Design and Implementation of Sequential Counters Using Reversible Logic Gates with Mach-Zehnder Interferometer A.Rudramadevi M.Tech(ES & VLSI Design),

7/03/2014 · IMPLEMENTATION OF BOOLEAN FUNCTIONS IN SUM OF PRODUCT FORM BY NAND GATES.

CMOS VLSI is thedigital implementation technology of choice for the foreseeable future (next 10-20 years) For other gates, Logical Effort is ratio of logic gate’s input 2 2 2 – –) – – – – – – –

International Journal of Advanced Technology in Engineering and Science www.ijates.com Volume No 03, Special Issue No. 01, March 2015 ISSN (online): 2348 – 7550

Digital Logic Design: Previous: AND OR NAND XOR XNOR Gate Implementation and Applications: Next >>> CS302 – Digital Logic & Design. Lesson No. 06. LOGIC GATES & OPERATIONAL CHARACTERISTICS. NOR Gate as a Universal Gate. The NOR gate is also used as a Universal Gate as the NOR Gate can be used in a. combination to perform the function of a AND, OR and NOT gates. 4. NOT Gate Implementation…

Chapter 6 Implementation of Logic Circuits with Standard Logic Chips Once logic circuits have been designed with generic logic devices, the next step is to implement the design in physical hardware. The first approach we will study is to use standard logic chips, integrated circuits that contain a small number of logic devices. The second approach, using programmable logic hardware, will be

The reversible logic gates will be having n-input and n-output i.e. equal number of input and equal number of output, and also with one-to-one mapping i.e. inputs can …

The implementation of all optical NAND logic gate is one of the most important aspects. The universal logic gate is one of the most essential logic gates. Hence, it is interesting to implement the NAND logic functionality in the optical domain using the micro-ring resonator structure. However, the symbol and truth table of NAND logic gate can be represented by the Fig.

A reversible gate has the equal number of inputs and outputs and one-to-one mappings between input vectors and output vector, thus the vector of input states can be always reconstructed from the vector of output states. A gate with k inputs and k outputs is called a k*k gate. Reversible logic Gate has one of the most important approaches for the power factor with its application in low power

Reversible implementation is done using a BVPPG gate, three Peres gates and a Feynman gate as shown in fig 5. BVPPG gate generates two partial products among which, one is Q0. Q1 is obtained from one of the Peres gates and Q2, Q3 are the outputs from Feynman gate. This design needs five reversible logic gates, five constant inputs and generates five garbage outputs. Quantum cost and …

Journal of Network Communications and Emerging Technologies (JNCET) www.jncet.org Volume 6, Issue 12, December (2016) ISSN: 2395-5317 ©EverScience Publications 20

Steps to be followed in the process of implementation of Logic Gates: Step 1: For NAND implementation, add Bubbles at the outputs of AND gates and at the inputs of OR gates.

Chapter 6 Implementation of Logic Circuits with Standard

Multiplexer/Decoder Implementation of Logic Functions

Memristor-CMOS (MeMOS) logic based adder circuit that can be used in based logic computational architectures. I I have also analyzed the transient response of logic gates designed using MeMOS logic …

implementation of logic gates using mux Q- Using 2 to 1 MUX implement the following 2-input gates: (a) OR (b) AND (c) NOR (d) NAND (e) XOR (f) XNOR (g) NOT. Ans: To implement the above for every gate, either we can derive the different gates using the logic (the truth table) or the procedure to implement any function with MUX (discussed earlier)

A.Veera Lakshmi et al Low Power Implementation of Sequential Circuits using Reversible Logic Gates

3 Electronic Science Digital Electronics 5. Logic gates • ON or OFF describes the switch position. The common use of logic gate is to act as switches (although they have no moving parts).

Journal of Network Communications and Emerging Technologies (JNCET) www.jncet.org Volume 6, Issue 12, December (2016) ISSN: 2395-5317 ©EverScience Publications 20

Experiment 2 Basic Logic Gates Implementation Using Breadboards and Discrete Gates Introduction:Introduction: Logic functions can be implemented in several ways.

that when the data select input, A is LOW at logic 0, input I1 passes its data through the NAND gate multiplexer circuit to the output, while input I0 is

Implementation of Advanced encryption Standard using Reversible Logic Gate D Srinivas1, Boda Aruna2, Ravi Boda3 1 Department of ECE, VJIT, Hyderabad, India 2 Department of ECE, MIETW, Hyderabad, India 2Department ECE, University College of Engineering, Osmania University, India Abstract: The Rijndael cryptosystem is a new Advanced Encryption Standard (AES) till now many …

designed the various Domino logic gates such as AND, OR, NAND, NOR and here we have analyzed the performance of these gates in the terms of number of transistors, area, and Power.

IMPLEMENTATION OF VEDIC ULTIPLIER USING REVERSIBLE GATES

NOR logic Wikipedia

– practicing the implementation of multiple input AND and OR functions using degenerate two-level logic circuit forms, – gaining a close insight into the functioning and properties of decoder circuits,

present the simulation of NAND and NOR logic gate by CMOS and PFAL logic moreover with the help of simulated result by OrCAD PSPICE tool, it can be shown that the NAND & NOR used with adiabatic logic can reduce the power dissipation effectively than conventional CMOS circuit. Key Words: Low Power, Adiabatic Circuits, Logic Gates. 1. INTRODUCTION With the cultivation of VLSI technology …

Page 191 Design and Implementation of Sequential Counters Using Reversible Logic Gates with Mach-Zehnder Interferometer A.Rudramadevi M.Tech(ES & VLSI Design),

that when the data select input, A is LOW at logic 0, input I1 passes its data through the NAND gate multiplexer circuit to the output, while input I0 is

Reversible implementation is done using a BVPPG gate, three Peres gates and a Feynman gate as shown in fig 5. BVPPG gate generates two partial products among which, one is Q0. Q1 is obtained from one of the Peres gates and Q2, Q3 are the outputs from Feynman gate. This design needs five reversible logic gates, five constant inputs and generates five garbage outputs. Quantum cost and …

The reversible logic gates will be having n-input and n-output i.e. equal number of input and equal number of output, and also with one-to-one mapping i.e. inputs can …

Implementation of Advanced encryption Standard using Reversible Logic Gate D Srinivas1, Boda Aruna2, Ravi Boda3 1 Department of ECE, VJIT, Hyderabad, India 2 Department of ECE, MIETW, Hyderabad, India 2Department ECE, University College of Engineering, Osmania University, India Abstract: The Rijndael cryptosystem is a new Advanced Encryption Standard (AES) till now many …

designed the various Domino logic gates such as AND, OR, NAND, NOR and here we have analyzed the performance of these gates in the terms of number of transistors, area, and Power.

International Journal of Advanced Technology in Engineering and Science www.ijates.com Volume No 03, Special Issue No. 01, March 2015 ISSN (online): 2348 – 7550

logic gates using Taffoli gates. The architecture of binary multiplier is specially designed to make them suitable The architecture of binary multiplier is specially designed to make them suitable for reversible logic implementation.

The action of the c-NOT logic gate is to swap two of the spin populations. Logic gates such as these, which can be expressed as a truth table and which are unitary, are necessarily permu-

3 Electronic Science Digital Electronics 5. Logic gates • ON or OFF describes the switch position. The common use of logic gate is to act as switches (although they have no moving parts).

4 × 4 bit Vedic multipliers using reversible logic gate. Design and implementation of 2 × 2 and 4 × 4 bit vedic multiplier using irreversible logic gates Vedic multiplier technique is used to perform multiplication operation in a faster way as compared to usual multiplication approach. In this paper we tried to implement the same not using irreversible gates but with reversible gates [5-7

The basic logic gates can be combined to form more complex digital circuits of all types. In fact, the NOT and AND gates alone are sufficient, but that does not really concern us… Computer Science Dept Va Tech October 2003 ©2003 McQuain WD & Keller BJ Logic Gates 3 OO Software Design and Construction Modeling a Logic Gate Consider the fundamental characteristics of the logic gates …

Design and Implementation of Sequential Counters Using

Vol. 5 Issue 5 May 2016 Design and Implementation of CLA

Digital Logic Design: Previous: AND OR NAND XOR XNOR Gate Implementation and Applications: Next >>> CS302 – Digital Logic & Design. Lesson No. 06. LOGIC GATES & OPERATIONAL CHARACTERISTICS. NOR Gate as a Universal Gate. The NOR gate is also used as a Universal Gate as the NOR Gate can be used in a. combination to perform the function of a AND, OR and NOT gates. 4. NOT Gate Implementation…

Page 191 Design and Implementation of Sequential Counters Using Reversible Logic Gates with Mach-Zehnder Interferometer A.Rudramadevi M.Tech(ES & VLSI Design),

Ternary logic gates are the basic building blocks in realizing combinational and sequential logic functions. The implementation is based around (bipolar transistors, MOSFETs etc.) a basic switching elements, which is referred to as T-Gates . The Ternary gate called T-gate qualifies as a universal element in several different senses. Firstly, it should be logically complete with simple

Implementation of threshold logic gates using RTDs Journal of Electronic and Electrical Engineering, ISSN: 0976–8106 & E-ISSN: 0976–8114, Vol. 1, Issue 2, 2010

Implementation of Advanced encryption Standard using Reversible Logic Gate D Srinivas1, Boda Aruna2, Ravi Boda3 1 Department of ECE, VJIT, Hyderabad, India 2 Department of ECE, MIETW, Hyderabad, India 2Department ECE, University College of Engineering, Osmania University, India Abstract: The Rijndael cryptosystem is a new Advanced Encryption Standard (AES) till now many …

The reversible logic gates will be having n-input and n-output i.e. equal number of input and equal number of output, and also with one-to-one mapping i.e. inputs can …

Memristor-CMOS (MeMOS) logic based adder circuit that can be used in based logic computational architectures. I I have also analyzed the transient response of logic gates designed using MeMOS logic …

Combinational Logic Implementation z Two-level logic y Implementations of two-level logic y NAND/NOR z Multi-level logic y Factored forms y And-or-invert gates z Time behavior y Gate delays y Hazards z Regular logic y Multiplexers y Decoders y PAL/PLAs y ROMs CS 150 – Sringp 0012 – Combinational Implementionta – 2 Implementations of Two-level Logic z Sum-of-products y AND gates …

The basic logic gates can be combined to form more complex digital circuits of all types. In fact, the NOT and AND gates alone are sufficient, but that does not really concern us… Computer Science Dept Va Tech October 2003 ©2003 McQuain WD & Keller BJ Logic Gates 3 OO Software Design and Construction Modeling a Logic Gate Consider the fundamental characteristics of the logic gates …

present the simulation of NAND and NOR logic gate by CMOS and PFAL logic moreover with the help of simulated result by OrCAD PSPICE tool, it can be shown that the NAND & NOR used with adiabatic logic can reduce the power dissipation effectively than conventional CMOS circuit. Key Words: Low Power, Adiabatic Circuits, Logic Gates. 1. INTRODUCTION With the cultivation of VLSI technology …

A reversible gate has the equal number of inputs and outputs and one-to-one mappings between input vectors and output vector, thus the vector of input states can be always reconstructed from the vector of output states. A gate with k inputs and k outputs is called a k*k gate. Reversible logic Gate has one of the most important approaches for the power factor with its application in low power

VHDL Implementation of 4-Bit Full Adder Using Reversible

Construction and Implementation of NMR Quantum Logic Gates

A NOR gate is a logic gate which gives a positive output only when both inputs are negative. Like NAND gates, NOR gates are so-called “universal gates” that can be combined to form any other kind of logic gate.

– practicing the implementation of multiple input AND and OR functions using degenerate two-level logic circuit forms, – gaining a close insight into the functioning and properties of decoder circuits,

Page 191 Design and Implementation of Sequential Counters Using Reversible Logic Gates with Mach-Zehnder Interferometer A.Rudramadevi M.Tech(ES & VLSI Design),

Diode logic gates use diodes to perform OR and AND logic functions as shown in the circuit diagram. Connection of the LED at the output is optional which simply displays

7/03/2014 · IMPLEMENTATION OF BOOLEAN FUNCTIONS IN SUM OF PRODUCT FORM BY NAND GATES.

4 × 4 bit Vedic multipliers using reversible logic gate. Design and implementation of 2 × 2 and 4 × 4 bit vedic multiplier using irreversible logic gates Vedic multiplier technique is used to perform multiplication operation in a faster way as compared to usual multiplication approach. In this paper we tried to implement the same not using irreversible gates but with reversible gates [5-7

International Journal of Advanced Technology in Engineering and Science www.ijates.com Volume No 03, Special Issue No. 01, March 2015 ISSN (online): 2348 – 7550

A reversible gate has the equal number of inputs and outputs and one-to-one mappings between input vectors and output vector, thus the vector of input states can be always reconstructed from the vector of output states. A gate with k inputs and k outputs is called a k*k gate. Reversible logic Gate has one of the most important approaches for the power factor with its application in low power

QCA cell-based structures can implement the logic gates, wires, memory units, combinational and sequential logic circuits. Digital logic design employing QCA cell is the main focus of this paper. In this paper, structure for Exclusive OR operation is proposed with primary goal of application in adder circuit to reduce the area. QCA designer is the EDA tool used for implementation and

The XOR and XNOR logic gates implementation consists of two MZI structures as shown in Fig. 3. The continuous optical signal of wavelength λ is applied at the input port of MZI 1. Here, no signal is provided at the second input terminal of MZI 1.

Digital Logic Design: Previous: AND OR NAND XOR XNOR Gate Implementation and Applications: Next >>> CS302 – Digital Logic & Design. Lesson No. 06. LOGIC GATES & OPERATIONAL CHARACTERISTICS. NOR Gate as a Universal Gate. The NOR gate is also used as a Universal Gate as the NOR Gate can be used in a. combination to perform the function of a AND, OR and NOT gates. 4. NOT Gate Implementation…

Journal of Network Communications and Emerging Technologies (JNCET) www.jncet.org Volume 6, Issue 12, December (2016) ISSN: 2395-5317 ©EverScience Publications 20

Implementation of Ternary Logic Gates using CNTFET Rahul A. Kashyap1 1 fundamental gates in a ternary logic system are the inverter, NOR and NAND gates respectively. The ternary logic levels and values are shown in Table I. Voltage Level Logic Value 0 0 1/2V dd 1 V dd 2 Table. 1 : Logic Values A. Ternary Inverter A Ternary Inverter is a fundamental gate in ternary logic system. A general

3 Electronic Science Digital Electronics 5. Logic gates • ON or OFF describes the switch position. The common use of logic gate is to act as switches (although they have no moving parts).

The basic logic gates can be combined to form more complex digital circuits of all types. In fact, the NOT and AND gates alone are sufficient, but that does not really concern us… Computer Science Dept Va Tech October 2003 ©2003 McQuain WD & Keller BJ Logic Gates 3 OO Software Design and Construction Modeling a Logic Gate Consider the fundamental characteristics of the logic gates …

Design and Implementation of Vedic Multipliers Using

VHDL Implementation of Reversible Logic Gates

2b. The implementation of a NAND gate is shown in Fig 2c. An OR gate is realized by connecting two new reversible gates as shown in the Fig 2d shown in the Fig 2d.

The implementation of all optical NAND logic gate is one of the most important aspects. The universal logic gate is one of the most essential logic gates. Hence, it is interesting to implement the NAND logic functionality in the optical domain using the micro-ring resonator structure. However, the symbol and truth table of NAND logic gate can be represented by the Fig.

The XOR and XNOR logic gates implementation consists of two MZI structures as shown in Fig. 3. The continuous optical signal of wavelength λ is applied at the input port of MZI 1. Here, no signal is provided at the second input terminal of MZI 1.

Memristor-CMOS (MeMOS) logic based adder circuit that can be used in based logic computational architectures. I I have also analyzed the transient response of logic gates designed using MeMOS logic …

In this paper, Threshold logic gates (TLG) are implemented using Resonant Tunneling Diodes (RTD). TLG is conceptually similar to the early McCulloch-Pitts model of the neuron and is normally used

explorerootsimplementation of logic gates using MUX

NOR logic Wikipedia

QCA cell-based structures can implement the logic gates, wires, memory units, combinational and sequential logic circuits. Digital logic design employing QCA cell is the main focus of this paper. In this paper, structure for Exclusive OR operation is proposed with primary goal of application in adder circuit to reduce the area. QCA designer is the EDA tool used for implementation and

The action of the c-NOT logic gate is to swap two of the spin populations. Logic gates such as these, which can be expressed as a truth table and which are unitary, are necessarily permu-

But with the applications of Boolean gates like Adders, Subtractors, Counters and so on it is possible to create almost any logic. With this post, we are going to help you and thus understand better, the logic behind using gates. The steps are simple and creative. But for the implementation requires a relay and a 6 volt battery. The very first implementation of Boolean gates also included

There are many types of reversible logic gates currently being used .eg fennyman gate, toffoli gate, peres gate etc. For our implementation we have used Peres reversible logic gate.

Page 191 Design and Implementation of Sequential Counters Using Reversible Logic Gates with Mach-Zehnder Interferometer A.Rudramadevi M.Tech(ES & VLSI Design),

present the simulation of NAND and NOR logic gate by CMOS and PFAL logic moreover with the help of simulated result by OrCAD PSPICE tool, it can be shown that the NAND & NOR used with adiabatic logic can reduce the power dissipation effectively than conventional CMOS circuit. Key Words: Low Power, Adiabatic Circuits, Logic Gates. 1. INTRODUCTION With the cultivation of VLSI technology …

Experiment 2 Basic Logic Gates Implementation Using Breadboards and Discrete Gates Introduction:Introduction: Logic functions can be implemented in several ways.

A.Veera Lakshmi et al Low Power Implementation of Sequential Circuits using Reversible Logic Gates

2b. The implementation of a NAND gate is shown in Fig 2c. An OR gate is realized by connecting two new reversible gates as shown in the Fig 2d shown in the Fig 2d.

Journal of Network Communications and Emerging Technologies (JNCET) www.jncet.org Volume 6, Issue 12, December (2016) ISSN: 2395-5317 ©EverScience Publications 20

The XOR and XNOR logic gates implementation consists of two MZI structures as shown in Fig. 3. The continuous optical signal of wavelength λ is applied at the input port of MZI 1. Here, no signal is provided at the second input terminal of MZI 1.

Design and Implementation of Adiabatic based Low Power

VHDL Implementation of Reversible Logic Gates

2/01/2017 · IMPLEMENTATION OF BOOLEAN EXPRESSION USING UNIVERSAL GATES(NAND/NOR) GATE BUS ADDA. Loading… Unsubscribe from GATE BUS ADDA? Cancel Unsubscribe. Working… Subscribe Subscribed Unsubscribe 8.7K

Steps to be followed in the process of implementation of Logic Gates: Step 1: For NAND implementation, add Bubbles at the outputs of AND gates and at the inputs of OR gates.

Memristor-CMOS (MeMOS) logic based adder circuit that can be used in based logic computational architectures. I I have also analyzed the transient response of logic gates designed using MeMOS logic …

A.Veera Lakshmi et al Low Power Implementation of Sequential Circuits using Reversible Logic Gates

3 Electronic Science Digital Electronics 5. Logic gates • ON or OFF describes the switch position. The common use of logic gate is to act as switches (although they have no moving parts).

designed the various Domino logic gates such as AND, OR, NAND, NOR and here we have analyzed the performance of these gates in the terms of number of transistors, area, and Power.

In this paper, Threshold logic gates (TLG) are implemented using Resonant Tunneling Diodes (RTD). TLG is conceptually similar to the early McCulloch-Pitts model of the neuron and is normally used

Ternary logic gates are the basic building blocks in realizing combinational and sequential logic functions. The implementation is based around (bipolar transistors, MOSFETs etc.) a basic switching elements, which is referred to as T-Gates . The Ternary gate called T-gate qualifies as a universal element in several different senses. Firstly, it should be logically complete with simple

– practicing the implementation of multiple input AND and OR functions using degenerate two-level logic circuit forms, – gaining a close insight into the functioning and properties of decoder circuits,

Combinational Logic Implementation z Two-level logic y Implementations of two-level logic y NAND/NOR z Multi-level logic y Factored forms y And-or-invert gates z Time behavior y Gate delays y Hazards z Regular logic y Multiplexers y Decoders y PAL/PLAs y ROMs CS 150 – Sringp 0012 – Combinational Implementionta – 2 Implementations of Two-level Logic z Sum-of-products y AND gates …

4 × 4 bit Vedic multipliers using reversible logic gate. Design and implementation of 2 × 2 and 4 × 4 bit vedic multiplier using irreversible logic gates Vedic multiplier technique is used to perform multiplication operation in a faster way as compared to usual multiplication approach. In this paper we tried to implement the same not using irreversible gates but with reversible gates [5-7

QCA cell-based structures can implement the logic gates, wires, memory units, combinational and sequential logic circuits. Digital logic design employing QCA cell is the main focus of this paper. In this paper, structure for Exclusive OR operation is proposed with primary goal of application in adder circuit to reduce the area. QCA designer is the EDA tool used for implementation and

Implementation of Advanced encryption Standard using

Realization of Logic Gates Using Universal Gates Testbook

4 × 4 bit Vedic multipliers using reversible logic gate. Design and implementation of 2 × 2 and 4 × 4 bit vedic multiplier using irreversible logic gates Vedic multiplier technique is used to perform multiplication operation in a faster way as compared to usual multiplication approach. In this paper we tried to implement the same not using irreversible gates but with reversible gates [5-7

III.1A Digital logic gates Combinational Digital gates are circuits that pass or block signals moving through a logic circuit. NOT gate Fig. 9 XOR design with NAND and NOR gates 1 Hence the following implementation constitutes a half adder circuit. A 1 B 1 A 1 B 1 A B 1 A 1 B 1 A B 1 1 C1 S1 Fig. 10 Half adder circuit. FULL ADDER Task: Build the circuit below and verify that it works as a

CMOS VLSI is thedigital implementation technology of choice for the foreseeable future (next 10-20 years) For other gates, Logical Effort is ratio of logic gate’s input 2 2 2 – –) – – – – – – –

7/03/2014 · IMPLEMENTATION OF BOOLEAN FUNCTIONS IN SUM OF PRODUCT FORM BY NAND GATES.

Boolean logic in the form of simple gates is very straightforward. From simple gates you can create more complicated functions, like addition. Physically implementing the gates is possible and easy. From those three facts you have the heart of the digital revolution, and you understand, at the core, how computers work.

Diode logic gates use diodes to perform OR and AND logic functions as shown in the circuit diagram. Connection of the LED at the output is optional which simply displays

Chapter 6 Implementation of Logic Circuits with Standard Logic Chips Once logic circuits have been designed with generic logic devices, the next step is to implement the design in physical hardware. The first approach we will study is to use standard logic chips, integrated circuits that contain a small number of logic devices. The second approach, using programmable logic hardware, will be

The XOR and XNOR logic gates implementation consists of two MZI structures as shown in Fig. 3. The continuous optical signal of wavelength λ is applied at the input port of MZI 1. Here, no signal is provided at the second input terminal of MZI 1.

/International Journal Of Computational Engineering

Design and Implementation of Domino Logic Circuit in CMOS

International Journal of Advanced Technology & Engineering Research (IJATER) ISSN NO: 2250-3536 VOLUME 2, ISSUE 3, MAY 2012 158

Implementation of Advanced encryption Standard using Reversible Logic Gate D Srinivas1, Boda Aruna2, Ravi Boda3 1 Department of ECE, VJIT, Hyderabad, India 2 Department of ECE, MIETW, Hyderabad, India 2Department ECE, University College of Engineering, Osmania University, India Abstract: The Rijndael cryptosystem is a new Advanced Encryption Standard (AES) till now many …

CprE 210 Lec 15 1 • Multiplexers are circuits which select one of many inputs • In here, we assume that we have one-bit inputs (in general, each input may have more than one bit)

A reversible gate has the equal number of inputs and outputs and one-to-one mappings between input vectors and output vector, thus the vector of input states can be always reconstructed from the vector of output states. A gate with k inputs and k outputs is called a k*k gate. Reversible logic Gate has one of the most important approaches for the power factor with its application in low power

There are many types of reversible logic gates currently being used .eg fennyman gate, toffoli gate, peres gate etc. For our implementation we have used Peres reversible logic gate.

III.1A Digital logic gates Combinational Digital gates are circuits that pass or block signals moving through a logic circuit. NOT gate Fig. 9 XOR design with NAND and NOR gates 1 Hence the following implementation constitutes a half adder circuit. A 1 B 1 A 1 B 1 A B 1 A 1 B 1 A B 1 1 C1 S1 Fig. 10 Half adder circuit. FULL ADDER Task: Build the circuit below and verify that it works as a

Design and Implementation of Domino Logic Circuit in CMOS

Implementation Technologies University of Washington

2b. The implementation of a NAND gate is shown in Fig 2c. An OR gate is realized by connecting two new reversible gates as shown in the Fig 2d shown in the Fig 2d.

implementation of logic gates using mux Q- Using 2 to 1 MUX implement the following 2-input gates: (a) OR (b) AND (c) NOR (d) NAND (e) XOR (f) XNOR (g) NOT. Ans: To implement the above for every gate, either we can derive the different gates using the logic (the truth table) or the procedure to implement any function with MUX (discussed earlier)

Diode logic gates use diodes to perform OR and AND logic functions as shown in the circuit diagram. Connection of the LED at the output is optional which simply displays

Realization of Logic Gates Using Mcculloch-Pitts Neuron Model J.S.Srinivas Raju1, Satish Kumar2, logic gate performances by using MCP model easily process of making and braking connections in Network solutions and solution of Hebb nets for REFERENCES [1] Neural Networks, Fuzzy Logic, and Genetic Algorithms by S.Rajasekharan and G.A Vijayalakshmi Pai. [2] OR GATE, Hyperphysics.phy …

IMPLEMENTATION OF BOOLEAN FUNCTIONS IN SUM OF

VHDL Implementation of 4-Bit Full Adder Using Reversible

Reversible implementation is done using a BVPPG gate, three Peres gates and a Feynman gate as shown in fig 5. BVPPG gate generates two partial products among which, one is Q0. Q1 is obtained from one of the Peres gates and Q2, Q3 are the outputs from Feynman gate. This design needs five reversible logic gates, five constant inputs and generates five garbage outputs. Quantum cost and …

Experiment 2 Basic Logic Gates Implementation Using Breadboards and Discrete Gates Introduction:Introduction: Logic functions can be implemented in several ways.

implementation of logic gates using mux Q- Using 2 to 1 MUX implement the following 2-input gates: (a) OR (b) AND (c) NOR (d) NAND (e) XOR (f) XNOR (g) NOT. Ans: To implement the above for every gate, either we can derive the different gates using the logic (the truth table) or the procedure to implement any function with MUX (discussed earlier)

377 Figure 1. Structured diagram of the logic gate minimisation package Figure 2. Minimised output expression and logic gate diagram

that when the data select input, A is LOW at logic 0, input I1 passes its data through the NAND gate multiplexer circuit to the output, while input I0 is

– practicing the implementation of multiple input AND and OR functions using degenerate two-level logic circuit forms, – gaining a close insight into the functioning and properties of decoder circuits,

Implementation Technologies University of Washington

AND OR NAND XOR XNOR Gate Implementation and

Reversible implementation is done using a BVPPG gate, three Peres gates and a Feynman gate as shown in fig 5. BVPPG gate generates two partial products among which, one is Q0. Q1 is obtained from one of the Peres gates and Q2, Q3 are the outputs from Feynman gate. This design needs five reversible logic gates, five constant inputs and generates five garbage outputs. Quantum cost and …

Journal of Network Communications and Emerging Technologies (JNCET) www.jncet.org Volume 6, Issue 12, December (2016) ISSN: 2395-5317 ©EverScience Publications 20

Experiment 2 Basic Logic Gates Implementation Using Breadboards and Discrete Gates Introduction:Introduction: Logic functions can be implemented in several ways.

QCA cell-based structures can implement the logic gates, wires, memory units, combinational and sequential logic circuits. Digital logic design employing QCA cell is the main focus of this paper. In this paper, structure for Exclusive OR operation is proposed with primary goal of application in adder circuit to reduce the area. QCA designer is the EDA tool used for implementation and

Implementation of Advanced encryption Standard using

IMPLEMENTATION OF VEDIC ULTIPLIER USING REVERSIBLE GATES

Diode logic gates use diodes to perform OR and AND logic functions as shown in the circuit diagram. Connection of the LED at the output is optional which simply displays

implementation of logic gates using mux Q- Using 2 to 1 MUX implement the following 2-input gates: (a) OR (b) AND (c) NOR (d) NAND (e) XOR (f) XNOR (g) NOT. Ans: To implement the above for every gate, either we can derive the different gates using the logic (the truth table) or the procedure to implement any function with MUX (discussed earlier)

Memristor-CMOS (MeMOS) logic based adder circuit that can be used in based logic computational architectures. I I have also analyzed the transient response of logic gates designed using MeMOS logic …

III.1A Digital logic gates Combinational Digital gates are circuits that pass or block signals moving through a logic circuit. NOT gate Fig. 9 XOR design with NAND and NOR gates 1 Hence the following implementation constitutes a half adder circuit. A 1 B 1 A 1 B 1 A B 1 A 1 B 1 A B 1 1 C1 S1 Fig. 10 Half adder circuit. FULL ADDER Task: Build the circuit below and verify that it works as a

Page 191 Design and Implementation of Sequential Counters Using Reversible Logic Gates with Mach-Zehnder Interferometer A.Rudramadevi M.Tech(ES & VLSI Design),

A reversible gate has the equal number of inputs and outputs and one-to-one mappings between input vectors and output vector, thus the vector of input states can be always reconstructed from the vector of output states. A gate with k inputs and k outputs is called a k*k gate. Reversible logic Gate has one of the most important approaches for the power factor with its application in low power

4 × 4 bit Vedic multipliers using reversible logic gate. Design and implementation of 2 × 2 and 4 × 4 bit vedic multiplier using irreversible logic gates Vedic multiplier technique is used to perform multiplication operation in a faster way as compared to usual multiplication approach. In this paper we tried to implement the same not using irreversible gates but with reversible gates [5-7

A.Veera Lakshmi et al Low Power Implementation of Sequential Circuits using Reversible Logic Gates

Digital Logic Design: Previous: AND OR NAND XOR XNOR Gate Implementation and Applications: Next >>> CS302 – Digital Logic & Design. Lesson No. 06. LOGIC GATES & OPERATIONAL CHARACTERISTICS. NOR Gate as a Universal Gate. The NOR gate is also used as a Universal Gate as the NOR Gate can be used in a. combination to perform the function of a AND, OR and NOT gates. 4. NOT Gate Implementation…

CMOS VLSI is thedigital implementation technology of choice for the foreseeable future (next 10-20 years) For other gates, Logical Effort is ratio of logic gate’s input 2 2 2 – –) – – – – – – –

A NOR gate is a logic gate which gives a positive output only when both inputs are negative. Like NAND gates, NOR gates are so-called “universal gates” that can be combined to form any other kind of logic gate.

logic gates using Taffoli gates. The architecture of binary multiplier is specially designed to make them suitable The architecture of binary multiplier is specially designed to make them suitable for reversible logic implementation.

Journal of Network Communications and Emerging Technologies (JNCET) www.jncet.org Volume 6, Issue 12, December (2016) ISSN: 2395-5317 ©EverScience Publications 20

2b. The implementation of a NAND gate is shown in Fig 2c. An OR gate is realized by connecting two new reversible gates as shown in the Fig 2d shown in the Fig 2d.

Design and Implementation of Boolean Functions using

Design and Implementation of Adiabatic based Low Power

Realization of Logic Gates Using Mcculloch-Pitts Neuron Model J.S.Srinivas Raju1, Satish Kumar2, logic gate performances by using MCP model easily process of making and braking connections in Network solutions and solution of Hebb nets for REFERENCES [1] Neural Networks, Fuzzy Logic, and Genetic Algorithms by S.Rajasekharan and G.A Vijayalakshmi Pai. [2] OR GATE, Hyperphysics.phy …

CMOS VLSI is thedigital implementation technology of choice for the foreseeable future (next 10-20 years) For other gates, Logical Effort is ratio of logic gate’s input 2 2 2 – –) – – – – – – –

CSEIT172551 Received : 10 Sep 2017 Accepted : 17 Sep 2017 September-October-2017 [(2)4: 243-247] International Journal of Scientific Research in Computer Science, …

III.1A Digital logic gates Combinational Digital gates are circuits that pass or block signals moving through a logic circuit. NOT gate Fig. 9 XOR design with NAND and NOR gates 1 Hence the following implementation constitutes a half adder circuit. A 1 B 1 A 1 B 1 A B 1 A 1 B 1 A B 1 1 C1 S1 Fig. 10 Half adder circuit. FULL ADDER Task: Build the circuit below and verify that it works as a

In this paper, Threshold logic gates (TLG) are implemented using Resonant Tunneling Diodes (RTD). TLG is conceptually similar to the early McCulloch-Pitts model of the neuron and is normally used

Diode logic gates use diodes to perform OR and AND logic functions as shown in the circuit diagram. Connection of the LED at the output is optional which simply displays

International Journal of Advanced Technology in Engineering and Science www.ijates.com Volume No 03, Special Issue No. 01, March 2015 ISSN (online): 2348 – 7550

CprE 210 Lec 15 1 • Multiplexers are circuits which select one of many inputs • In here, we assume that we have one-bit inputs (in general, each input may have more than one bit)

The basic logic gates can be combined to form more complex digital circuits of all types. In fact, the NOT and AND gates alone are sufficient, but that does not really concern us… Computer Science Dept Va Tech October 2003 ©2003 McQuain WD & Keller BJ Logic Gates 3 OO Software Design and Construction Modeling a Logic Gate Consider the fundamental characteristics of the logic gates …

that when the data select input, A is LOW at logic 0, input I1 passes its data through the NAND gate multiplexer circuit to the output, while input I0 is

logic gates using Taffoli gates. The architecture of binary multiplier is specially designed to make them suitable The architecture of binary multiplier is specially designed to make them suitable for reversible logic implementation.

Implementation of Ternary Logic Gates using CNTFET Rahul A. Kashyap1 1 fundamental gates in a ternary logic system are the inverter, NOR and NAND gates respectively. The ternary logic levels and values are shown in Table I. Voltage Level Logic Value 0 0 1/2V dd 1 V dd 2 Table. 1 : Logic Values A. Ternary Inverter A Ternary Inverter is a fundamental gate in ternary logic system. A general

implementation of logic gates using mux Q- Using 2 to 1 MUX implement the following 2-input gates: (a) OR (b) AND (c) NOR (d) NAND (e) XOR (f) XNOR (g) NOT. Ans: To implement the above for every gate, either we can derive the different gates using the logic (the truth table) or the procedure to implement any function with MUX (discussed earlier)

Chapter 6 Implementation of Logic Circuits with Standard Logic Chips Once logic circuits have been designed with generic logic devices, the next step is to implement the design in physical hardware. The first approach we will study is to use standard logic chips, integrated circuits that contain a small number of logic devices. The second approach, using programmable logic hardware, will be

designed the various Domino logic gates such as AND, OR, NAND, NOR and here we have analyzed the performance of these gates in the terms of number of transistors, area, and Power.

4 × 4 bit Vedic multipliers using reversible logic gate. Design and implementation of 2 × 2 and 4 × 4 bit vedic multiplier using irreversible logic gates Vedic multiplier technique is used to perform multiplication operation in a faster way as compared to usual multiplication approach. In this paper we tried to implement the same not using irreversible gates but with reversible gates [5-7

Design and Implementation of Basic Logic Gates and Adder

Design and Implementation of Boolean Functions using

Implementation of threshold logic gates using RTDs

QCA cell-based structures can implement the logic gates, wires, memory units, combinational and sequential logic circuits. Digital logic design employing QCA cell is the main focus of this paper. In this paper, structure for Exclusive OR operation is proposed with primary goal of application in adder circuit to reduce the area. QCA designer is the EDA tool used for implementation and

Implementing Gates Boolean Logic Implementation

Journal of Network Communications and Emerging Technologies (JNCET) http://www.jncet.org Volume 6, Issue 12, December (2016) ISSN: 2395-5317 ©EverScience Publications 20

Design and Implementation of Logic Gates using Artificial

The implementation of all optical NAND logic gate is one of the most important aspects. The universal logic gate is one of the most essential logic gates. Hence, it is interesting to implement the NAND logic functionality in the optical domain using the micro-ring resonator structure. However, the symbol and truth table of NAND logic gate can be represented by the Fig.

(PDF) Implementation of threshold logic gates using RTDs

Design and Implementation of Adiabatic based Low Power